## RAVE: RISC-V Analyzer of Vector Executions

### a QEMU tracing plugin

<u>Pablo Vizcaino,</u> Filippo Mantovani, Jesus Labarta, Roger Ferrer RISC-V Technical Session, October 10th

#### First half:

- Background on RVV

- EPAC chip

- Simulation environment

- Why do we need RAVE?

- How does RAVE work?

- Performance and use cases

#### Second half:

RAVE demo

#### Motivation

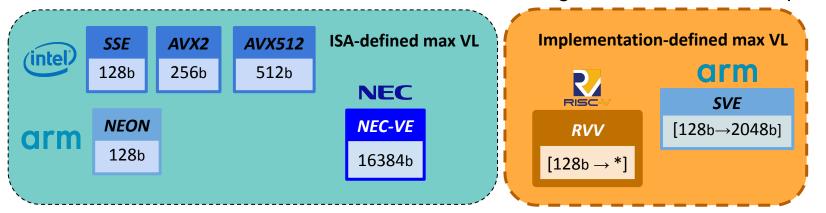

- **RVV** (RISC-V Vector extension) is RV's bet for High Performance Computing

#### Motivation

RVV (RISC-V Vector extension) is RV's bet for High Performance Computing

#### Motivation

RVV (RISC-V Vector extension) is RV's bet for High Performance Computing

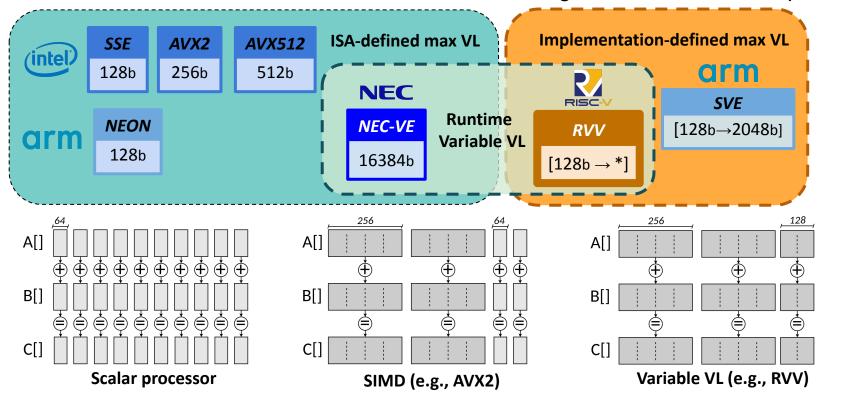

#### European Processor Initiative

### Who is implementing this technology?

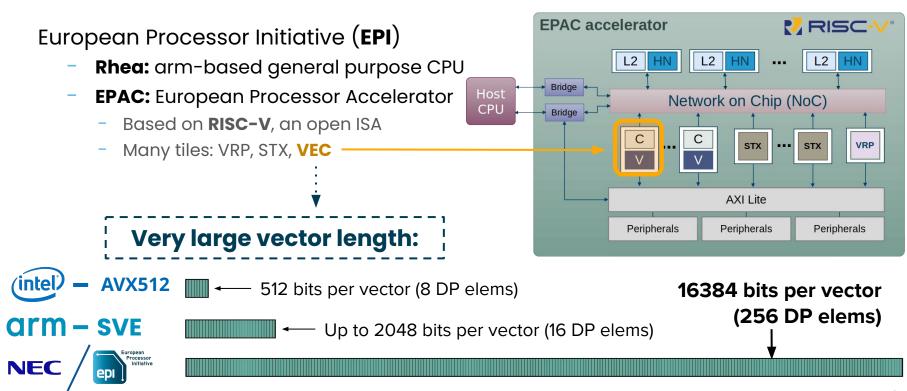

### How can you develop code for this accelerator?

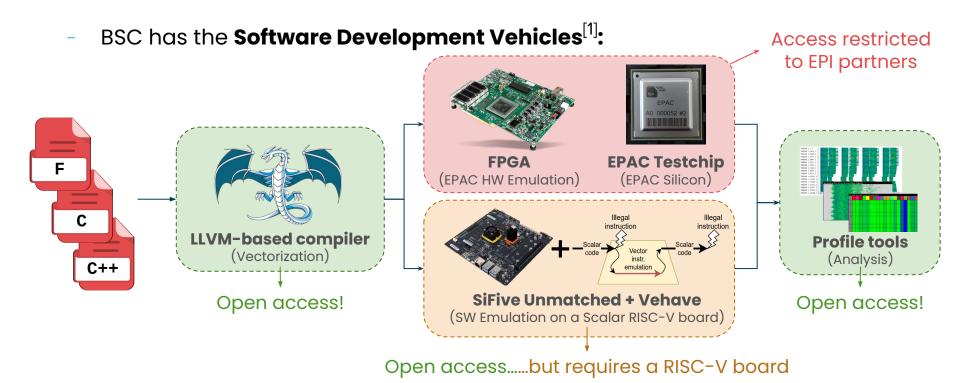

BSC has the Software Development Vehicles (SDV)<sup>[1]</sup>:

#### European Processor Initiative

### How can you develop code for this accelerator?

[1] Filippo Mantovani et al. (2023, May). Software Development Vehicles to enable extended and early co-design: a RISC-V and HPC case of study. In International Conference on High Performance Computing (pp. 526-537). Cham: Springer Nature Switzerland.

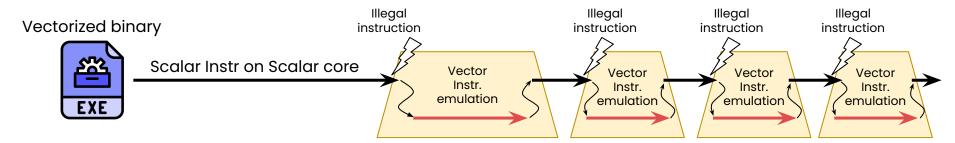

### Another issue with simulation (Vehave)

# epi European Processor Initiative

### Another issue with simulation (Vehave)

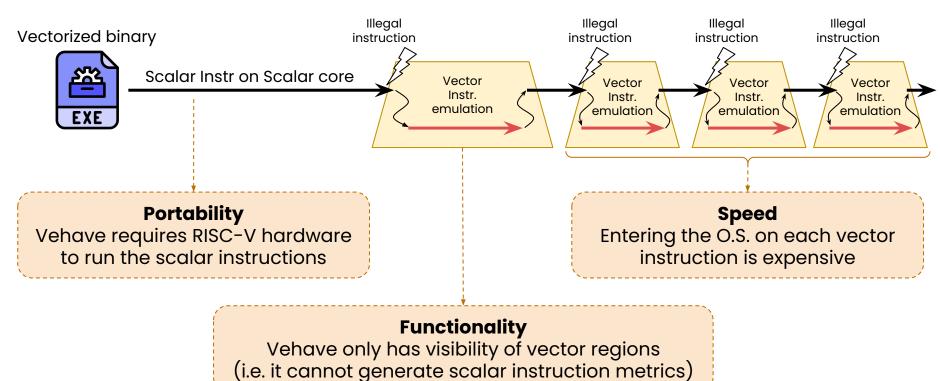

#### What is the alternative?

At the start of the EPI project, QEMU did not support RVV, but now it does!

#### Modifications to QEMU

- 1. Changing the **RV\_VLEN\_MAX** parameter in ./target/riscv/cpu.h:

- a. By default, it's 1024 bits —— we change it to 16384 bits (VLEN of EPAC)

#### Modifications to QEMU

- 1. Changing the **RV\_VLEN\_MAX** parameter in ./target/riscv/cpu.h:

- a. By default, it's **1024** bits we change it to **16384** bits (VLEN of EPAC)

- 2. Changing the size of the translation block to 1 instruction:

### RAVE plugin: RISC-V Analyzer of Vector Executions

We design a QEMU plugin to profile and analyze the vectorization:

#### **Matching Vehave functionalities**

- Print the sequence of executed vector instructions

- For each instruction, report:

- Vector Length (VL) and

- Element Width (8,16,32,64b)

- Length Multiplier (LMUL)

- Used Registers

- ...

- Provide an API called from the application code

- Create a PRV execution trace

### RAVE plugin: RISC-V Analyzer of Vector Executions

We design a QEMU plugin to profile and analyze the vectorization:

#### **Matching Vehave functionalities**

- Print the sequence of executed vector instructions

- For each instruction, report:

- Vector Length (VL) and

- Element Width (8,16,32,64b)

- Length Multiplier (LMUL)

- Used Registers

- ....

- Provide an API called from the application code

- Create a PRV execution trace

#### **Extend them in RAVE**

- Count the scalar instructions between vector ones

- Compute vectorization metrics on each instrumented block

- Generate a report at the end of the emulation to summarize these vector metrics

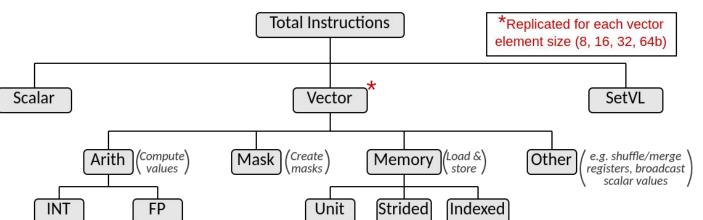

#### **Vectorization metrics**

We classify all instructions following this diagram:

```

#define SEWS 4

struct qemu_counters{

double scalar_instr;

double vsetvl_instr;

double vector_instr[SEWS];

double vunit_instr[SEWS];

double vstride_instr[SEWS];

double vidx_instr[SEWS];

double vfp_instr[SEWS];

double vint_instr[SEWS];

double vint_instr[SEWS];

double velem[SEWS];

}

```

- We derive metrics such as:

- VectorMix = Vector / Total\_Instructions

- V. Flop/Byte = Vector.Arith.FP / Vector.Memory

Emulation is transparent to applications, so they cannot call RAVE directly

- Emulation is transparent to applications, so they cannot call RAVE directly

- RAVE/QEMU only sees simulated instructions

- We must communicate through them...

- ... but without changing the program behavior

- Emulation is transparent to applications, so they cannot call RAVE directly

- RAVE/QEMU only sees simulated instructions

- We must communicate through them...

- ... but without changing the program behavior —— Use instructions writing to x0 (which is hardcoded to 0)

| User Function        | Instruction | Description                                  |

|----------------------|-------------|----------------------------------------------|

| rave_start_trace()   | li x0, −3   | After this instruction, tracing is enabled   |

| rave_stop_trace()    | li x0, -4   | After this instruction, tracing is disabled  |

| rave_restart_trace() | li x0, −2   | Deletes tracing information up to this point |

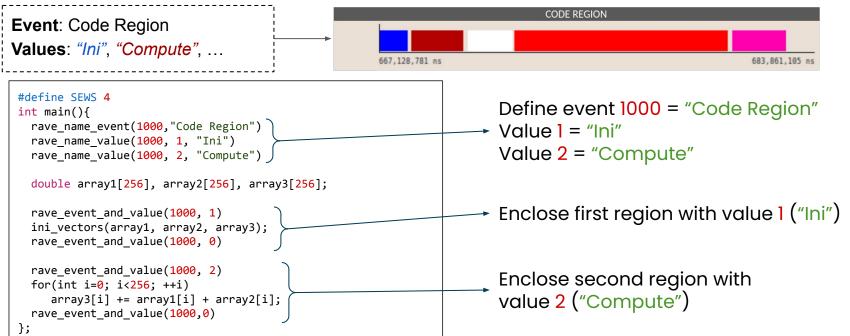

- We also add instrumentation mechanisms, to define regions of interest.

- We work with tuples of Events and Values:

These functionalities are also encoded in instructions writing to x0:

| User Function                              | Instruction                                                    | Description                                                                                                                                                 |  |  |

|--------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| rave_event_and_value(e,v)                  | or x0, src1, src2                                              | event <b>e</b> and value <b>v</b> are read from src1 and src2.                                                                                              |  |  |

| rave_name_event(e,name) and x0, src1, src2 |                                                                | src1 contains the event <b>e</b> , and src2 is equal to -1                                                                                                  |  |  |

|                                            | li x0, -1<br>lui x0, name[0],<br>lui x0, name[1],<br>li x0, -1 | The " <b>li x0, -1</b> " instructions mark the beginning and end of the name, and then a series of <b>lui</b> instructions encode its characters one by one |  |  |

| rave_name_value(e,v,name)                  | and x0, src1, src2                                             | src1 contains the event <b>e</b> , and src2 contains <b>v</b>                                                                                               |  |  |

|                                            | li x0, -1<br>lui x0, name[0],<br>lui x0, name[1],<br>li x0, -1 | The value name is transmitted using the same protocol as the event name.                                                                                    |  |  |

h1

### RAVE plugin flow (translation)

```

For each Instr ∈ translation_block

disassembly ← qemu_plugin_insn_disas(Instr)

enum instr type{SCALAR, VECTOR, VSETVL};

switch( type(disassembly) )

enum v major type{OTHER, ARITH, MEMORY, MASK};

enum v minor type{FP, INT, UNIT, STRIDE, INDEX};

struct instr data{

scalar:

uint64 t PC;

Instr_data ← fill_scalar_struct(Instr)

uint32 t paraver code;

char * asm string;

short dst, src1, src2, src3

Instr → set_callback(vcpu_insn_exec, Instr_data)

enum instr type type;

enum v major type v majortype;

vector:

enum v major type v minortype;

};

Instr_data ← fill_vec_struct(Instr)

Instr → set_callback(vcpu_insn_exec, Instr_data)

API/tracing:

Different callbacks for lix0, -1,

Function ← tracing_function(Instr) ___

and x0, src1, src2, etc...

Instr → set_callback(Function)

```

### RAVE plugin flow (execution callback)

```

callback vcpu_insn_exec(Instr_data):

//Trace and log

If (Instr_data.major_type == Vector){

read_cpu_state(VL, SEW)

log_instruction(Instr_data)

trace_instruction(Instr_data)

//counters

++total_instructions

If (Instr_data.major_type == Vector) ++vector_instructions

If (Instr_data.minor_type == V.Memory) ++vector_mem_instructions

//(....)

```

### RAVE plugin flow (execution callback)

```

callback vcpu_insn_exec(Instr_data):

//Trace and log

If (Instr_data.major_type == Vector){

read_cpu_state(VL, SEW)

Total Instructions

Replicated for each vector

log_instruction(Instr_data)

Scalar

Vector

SetVL

trace_instruction(Instr_data)

Mask (Create)

(Compute)

Memory

Strided

Indexed

//counters

++total_instructions

If (Instr_data.major_type == Vector) ++vector_instructions

If (Instr_data.minor_type == V.Memory) ++vector_mem_instructions

```

### **Evaluating RAVE**

#### We evaluate four setups/environments:

#### **Commodity Laptop** (QEMU+RAVE)

8-core Intel i7-8650U

2.1 GHz

16 GB

#### **Unmatched RISC-V board** (Vehave)

4-core HiFive Unmatched

1.2 GHz

16 GB

#### **High-end AMD node** (QEMU+RAVE)

12-core AMD Ryzen 5600G

3.9 GHz

32 GB

#### **Native execution** (FPGA)

EPAC RTL on VCU128 FPGA

50 MHz

4 GB

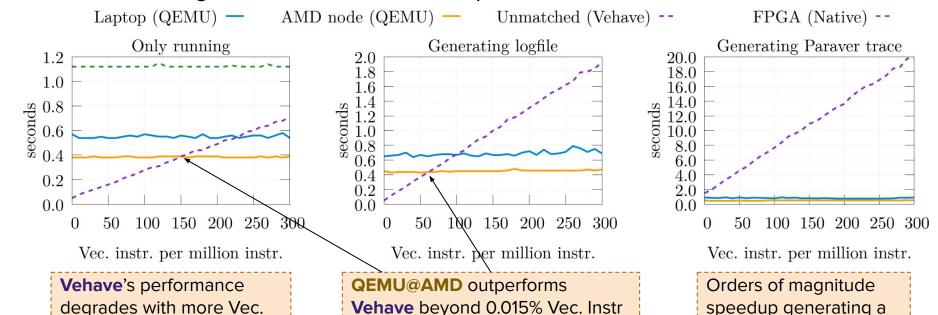

### Evaluating RAVE: Synthetic Benchmark

We measure the simulation time of a synthetic benchmark

- Increasing ratio of Vec. Instructions per Million total instructions (Scalar+Vec)

Laptop (QEMU) — AMD node (QEMU) — Unmatched (Vehave) --FPGA (Native) --Only running Generating logfile Generating Paraver trace 1.2 2.0 20.018.0 1.0 16.0 14.0seconds 0.8seconds seconds 12.0 10.0 0.80.6 6.0 0.44.00.20.0150 150250150Vec. instr. per million instr. Vec. instr. per million instr. Vec. instr. per million instr.

### Evaluating RAVE: Synthetic Benchmark

Instr (more O.S. overhead)

We measure the simulation time of a synthetic benchmark

- Increasing ratio of Vec. Instructions per Million total instructions (Scalar+Vec)

(or 0.005% when logging)

27

PRV trace.

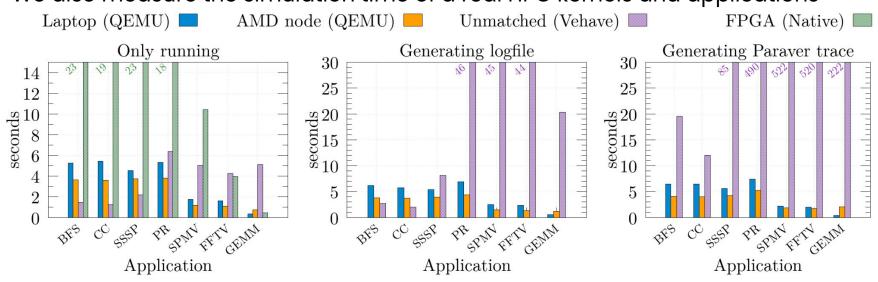

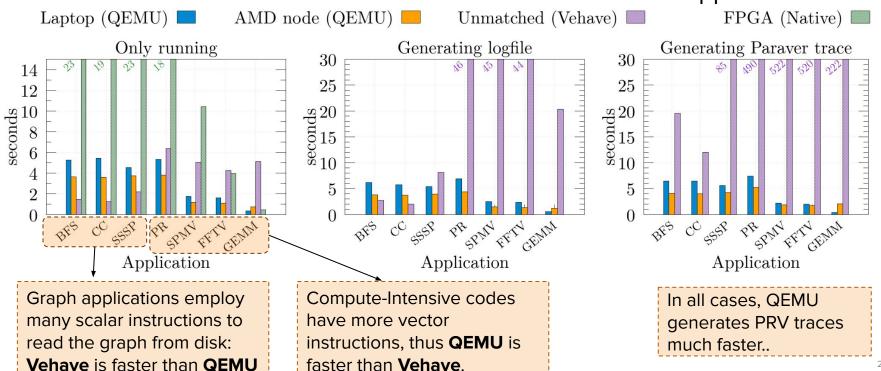

### **Evaluating RAVE: Real Applications**

We also measure the simulation time of a real HPC kernels and applications

### **Evaluating RAVE: Real Applications**

We also measure the simulation time of a real HPC kernels and applications

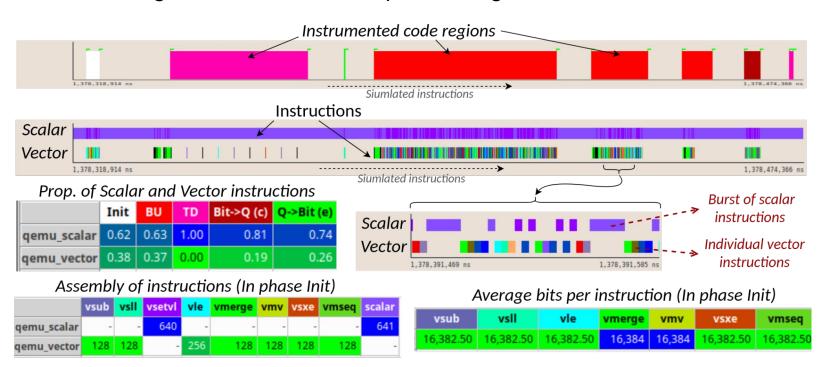

### Evaluating RAVE: Use case

Beside validating the vectorized binary, we can generate Vectorization Traces:

### Evaluating RAVE: Use case

#### Use trace insight to improve vectorization:

#### Before increasing TD Vectorization

|             | Init | BU   | TD   | Bit->Q (c) |

|-------------|------|------|------|------------|

| qemu_scalar | 0.62 | 0.63 | 1.00 | 0.81       |

| qemu_vector | 0.38 | 0.37 | 0.00 | 0.19       |

#### After increasing TD Vectorization

|             | Init | BU   | TD   | Bit->Q (c) |

|-------------|------|------|------|------------|

| qemu_scalar | 0.62 | 0.63 | 0.84 | 0.81       |

| qemu_vector | 0.38 | 0.37 | 0.16 | 0.19       |

#### Evaluating RAVE: Use case

You can also obtain vectorization metrics on a console report:

$(\ldots)$

```

your-machine$ rave ./bfs -f graph.el

(\ldots)

Reg. #3: Event 1000(code_region), Value 3(BU)

tot instr: 38872

scalar instr: 15818 (40.69 %)

vsetvl instr: 5236 (13.47 %)

SEW 64 vector instr: 17818 (45.84 %)

avg VL: 255.60 elements

Arith: 2466 (13.84 %)

FP: 0 (0.00 %)

INT: 2466 (100.00 %)

Mem: 3142 (17.63 %)

unit: 1573 (50.06 %)

strided: 0 (0.00 %)

indexed: 1569 (49.94 %)

Mask: 8171 (45.86 %)

Reduction in Mask and

Other: 4039 (22.67 %)

Other Vec Instructions

```

```

tot instr: 44780

scalar instr: 21866 (48.83 %)

vsetvl instr: 9556 (21.34 %)

SEW 64 vector instr: 13358 (29.83 %)

avg VL: 254.77 elements

Arith: 2481 (18.57 %)

FP: 0 (0.00 %)

INT: 2481 (100.00 %)

Mem: 3028 (22.67 %)

unit: 1454 (48.02 %)

strided: 0 (0.00 %)

indexed: 1574 (51.98 %)

Mask: 4992 (37.37 %)

Other: 2857 (21.39<u>%</u>)

```

your-machine\$ rave ./bfs no if -f graph.el

Reg. #3: Event 1000(code\_region), Value 3(BU)

# epi European Processor Initiative

#### Conclusions

- We developed a plugin for QEMU targeting the RISC-V Vector Extension

- We improved simulation framework of the EPI project:

- More accessible

- Faster

- Increased functionality

- RAVE is already being used by performance analysts at BSC

- Future work include:

- Selectively increasing the block size

- Further speeding up the plugin

- More functionalities (multi-core emulation, automatic instrumentation, ...)

## **SDV Vector Analysis Using RAVE**

Pablo Vizcaino RISC-V Technical Session, October 10th

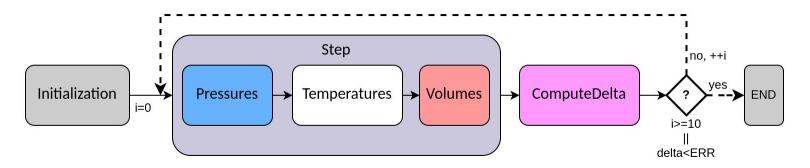

#### The Tutorial code

- **Main** function: Initialization of 2D arrays and a loop of 10 timesteps

- Each timestep calls:

- **Step** function: Works on three arrays, "Pressures", "Temperatures", and "Volumes"

- ComputeDelta function: Computes convergence of result

- This application is not physically-meaningful but contains common operations:

- Stencils, element-wise matrix operations, reductions, ...

Running on scalar commercial RISC-V boards Vectorization and RAVE-emulation on x86 boards

Natively running vector code on the EPAC RTL (FPGA)

- Introduction to our HPC system.

- Ensure the application runs in RISC-V.

- Code instrumentation and code region study

Running on scalar commercial RISC-V boards Vectorization and RAVE-emulation on x86 boards

Natively running vector code on the EPAC RTL (FPGA)

- Vectorize the application using the compiler capabilities

- Emulation and Tracing with RAVE

- Increasing and optimizing the vectorization

You can emulate the vectorized binary with RAVE:

```

laptop$ make reference-vec.x

laptop$ rave ./reference-vec.x

```

You can also instrument your code and generate reports of RAVE emulations:

```

laptop$ make reference-vec-instrument.x

laptop$ RAVE_PRINT_REPORT=1 rave ./reference-vec-instrument.x

```

Or generate Parave traces:

```

laptop$ RAVE_PRV_NAME=ref-vec rave

./reference-vec-instrument.x

```

```

Region#38: Event 1000(code region), Val 2(Temperatures)

Moved bytes (Total): 2054589

Moved bytes (scalar): 6589 (0.32 %)

Moved bytes (vector): 2048000 (99.68 %)

tot instr: 210148

scalar instr: 194148 (92.39 %)

vsetvl instr: 1600 (0.76 %)

vector instr: 14400 (6.85 %)

SEW 64 vector instr: 14400 (100.00 %)

avg VL: 32.00 elements

Arith: 6400 (44.44 %)

FP: 6400 (100.00 %)

Mem: 8000 (55.56 %)

unit: 8000 (100.00 %)

strided: 0 (0.00 %)

indexed: 0 (0.00 %)

Mask: 0 (0.00 %)

Other: 0 (0.00 %)

```

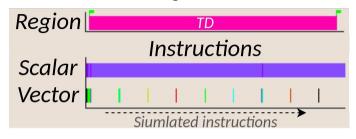

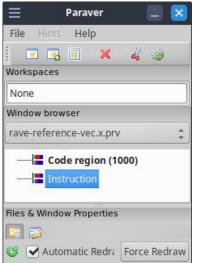

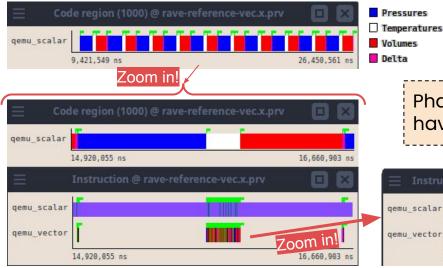

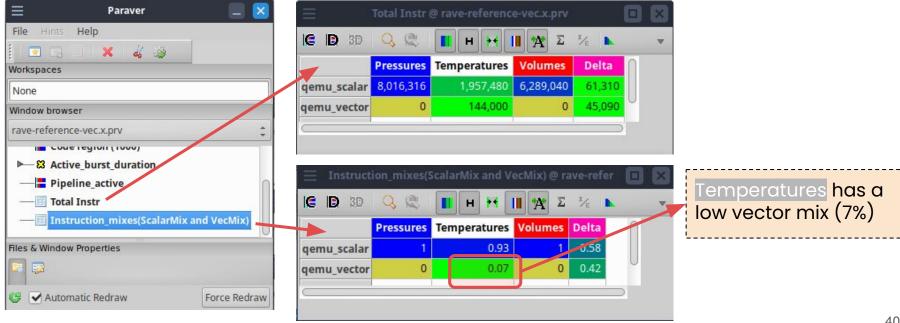

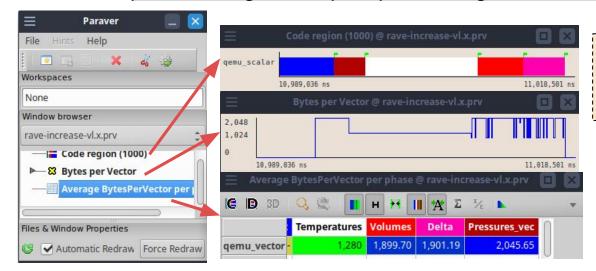

# 2.2 Running and tracing with RAVE

Open the traces with Paraver:

```

laptop$ wxparaver ref-vec.prv

```

Load the configuration files:

paraver\_cfgs/rave/per\_phase\_cfgs/event\_1000\_code\_region.cfg paraver\_cfgs/rave/Instruction\_timeline.cfg

Horizontal axis is "vec instructions", not "time"

Phases Pressures and Volumes have no vector instructions

#### European Initiative

# 2.2 Running and tracing with RAVE

Load the configuration file: paraver\_cfgs/rave/per\_phase\_cfgs/tables\_vector\_mix\_per\_phase.cfg

We can look at the compiler's warnings to find out why some phases are not vectorized:

- The Pressures phase cannot be vectorized due to the cbrt() function call.

- The Volumes phase has a problem with pointers and array bounds.

- For more information on compiler messages, refer to this FAQ

We can separate vectorizatiable and non-vectorizable work into two loops:

```

17 trace event and value(1000,1);

18 for(int i=0; i<N; ++i){

for(int j=0; j<M; ++j){</pre>

double length = (volumes[i*M+j]>1.0) ? cbrt(volumes[i*M+j]) : 0.5;

20

pressures[i*M+j] = length + (temperatures[i*M+j]-new_temperatures[i*M+j]);

trace_event_and_value(1000,1);

This loop will not vectorize

for(int i=0; i<N; ++i){</pre>

for(int j=0; j<M; ++j){ 4</pre>

pressures[i*M+j] = (volumes[i*M+j]>1.0) ? cbrt(volumes[i*M+j]) : 0.5;

trace event and value(1000,5)

for(int i=0; i<N; ++i){</pre>

This loop will vectorize

for(int j=0; j<M; ++j){</pre>

pressures[i*M+j] += (temperatures[i*M+j]-new_temperatures[i*M+j]);

const char * v names[]={"Other", "Pressures cbrt", "Temperatures",

"Volumes", "Delta", "Pressures vec"};

Added a new region!

int values[] = \{0,1,2,3,4,5\};

trace name event and values(1000, "code region", 6, values, v names);

```

# 2.3 Increasing vectorization (Volumes)

- The compiler "cannot identify array bounds".

- This means the compiler cannot assert the aliasing of the arrays/pointers.

- It normally occurs with indirected accesses

```

39 for(int i=0; i<N; ++i){

40    for(int j=0; j<M; ++j){

41        volumes[i*M+j] = pressures[bounds[i*M+j]] * new_temperatures[i*M+j];</pre>

```

It can be solved using a #pragma or declaring your array pointers as restrict

# 2.3 Increasing vectorization (Temperatures)

- The compiler does complain, and the aren't weird accesses or function calls

- We can make the loop more compiler-friendly with these three tricks:

- Change the induction variables type from int to long

- Add the #pragma clang loop vectorize(assume\_safety) on top of the vectorizable loop (or make pointers restrict)

- Move constant loop bounds known at compile time to defines (e.g. Block sizes)

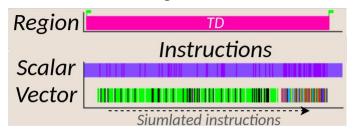

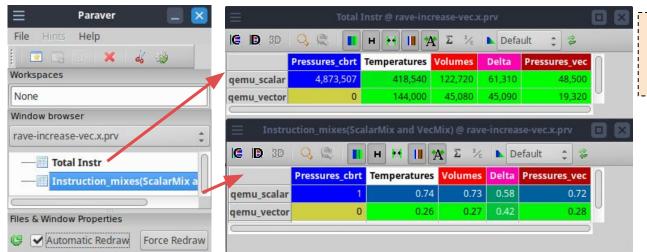

## 2.3 Increasing vectorization

Compile and trace the improved version SDV\_Tutorial/src/increase-vec.c

```

laptop$ make increase-vec.x

laptop$ RAVE_PRINT_REPORT=1 RAVE_PRV_NAME=inc-vec rave ./increase-vec.x

```

Open the traces with Paraver:

```

laptop$ wxparaver inc_vec.prv

```

Load paraver\_cfgs/rave/per\_phase\_cfgs/tables\_vector\_mix\_per\_phase.cfg

Only the non-vectorizable Pressures\_cbrt phase does not have vector instructions

Pressures\_vec reports good vector metrics

Load paraver\_cfgs/rave/per\_phase\_cfgs/table\_average\_vl\_per\_phase.cfg

Vector Length (Bytes) per instruction varies a lot in Volumes and Delta.

Average Vector Length (Bytes) in all phases far from **2048** Bytes/Vector (maximum in EPAC)

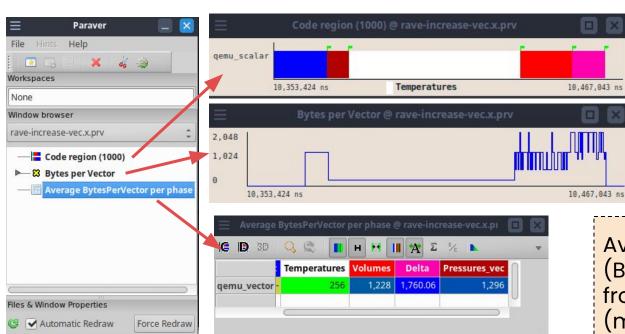

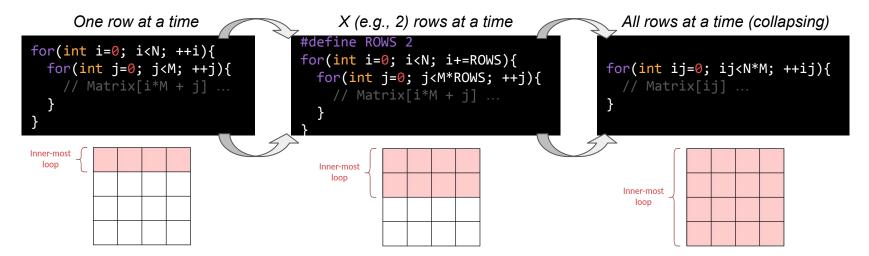

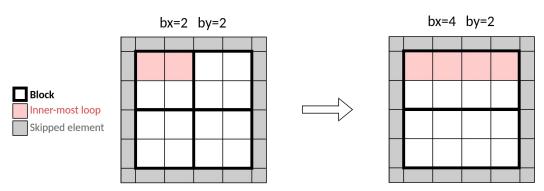

# 2.4 Increasing the Vector Length

- The vector length is limited by the bounds of the inner-most loops.

- In this code, inner-most loops go from j=0 to j=M-1, with M=162

- With double-precision data (64 bits), EPAC's vectors support up to 256 elems.

- The efficiency of the vector instructions grow with the vector length

- Solution: Increase inner-most loops bounds (collapsing loops)

# 2.4 Increasing the Vector Length

- We apply collapsing to phases Pressures\_vec, Volumes, Delta.

- Phase Temperatures presents a blocking structure.

- Normally intended to improve cache usage or vectorization on smaller extensions.

- Cannot collapse loops because edge elements should not be accessed in the stencil.

- We can increase the inner-most block size (bx) to match the columns' width to increase the vector length:

# 2.4 Increasing the Vector Length

Compile and trace the improved version SDV\_Tutorial/src/increase-vl.c

```

laptop$ make increase-vl.x

laptop$ RAVE PRINT_REPORT=1 RAVE_PRV_NAME=inc-vl rave ./increase-vl.x

```

Open the traces with Paraver:

```

laptop$ wxparaver inc-vl.prv

```

Load paraver\_cfgs/rave/per\_phase\_cfgs/table\_average\_vl\_per\_phase.cfg

Average Vector Length closer to **2048** Bytes/Vector (maximum in EPAC)

Temperatures increased from **256** to **1280**

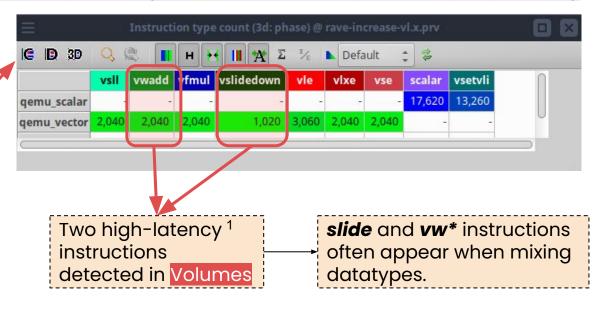

# 2.5 Avoid mixing datatypes

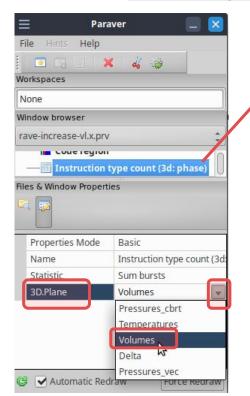

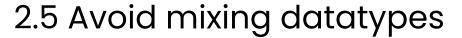

Load paraver\_cfgs/rave/per\_phase\_cfgs/table\_instruction\_type\_count\_per\_phase.cfg

<sup>&</sup>lt;sup>1</sup>Refer to the last slide (Annex) for latency estimates of vector instructions

#### European Processor Initiative

# 2.5 Avoid mixing datatypes

Phase 3 uses an array of integers to index an array of doubles:

- We recommend parameterizing the datatypes, to experiment with different sizes: typedef double T\_FP; //64b typedef long long T\_INT; //64b

- Solution in SDV\_Tutorial/src/flex-datatype.c. Compile it and trace it:

```

laptop$ make flex-datatype-i-vehave.x

laptop$ RAVE_PRINT_REPORT=1 RAVE_PRV_NAME=flex rave ./flex-datatype-i-vehave.x

```

Copy the traces back to your computer and open them in Paraver:

```

laptop$ wxparaver flex.prv

```

Load paraver\_cfgs/rave/per\_phase\_cfgs/table\_instruction\_type\_count\_per\_phase.cfg

**slide** and **vw\*** instructions no longer present on Volumes

vsetvli instructions reduced from 13k to 2k

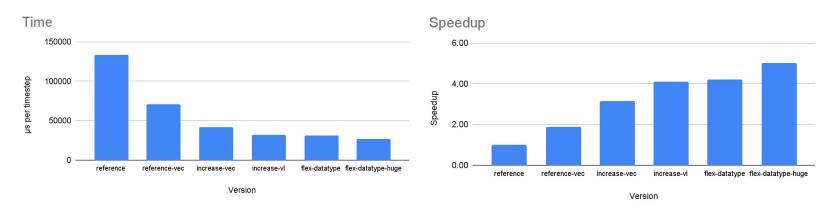

Running on scalar commercial RISC-V boards Vectorization and RAVE-emulation on x86 boards

Natively running vector code on the EPAC RTL (FPGA)

- Get time measurements

- Generate Extrae traces

- Further optimize the performance

- You can send binaries to the FPGA using the SLURM queue manager and the fpga\_job jobscript.

- Use the run\_all.sh script to run all versions and parse their outputs:

```

synth-hca$ sbatch fpga_job ./run_all.sh

Submitted batch job 189294

```

You can query the state of an FPGA job using the squeue command:

```

synth-hca$ squeue

JOBID PARTITION NAME USER ST TIME NODES NODELIST(REASON)

189294 fpga-sdv fpga_job user R 0:21 1 pickle-1

```

Job is running

### 3.1 Sending jobs to the FPGA nodes

When the job finishes, you can read its output file:

```

synth-hca$ cat slurm-189294.out

**********

* x86 node: pickle-1

* SDV node: fpga-sdv-1

**********

bash: warning: setlocale: LC_ALL: cannot change locale (en_US.UTF-8)

/bin/bash: warning: setlocale: LC ALL: cannot change locale (en US.UTF-8)

version

time per iteration

133090.00

reference.x

1.86x speedup

reference-vec.x 71180.30

increase-vec.x 42096.10

increase-vl.x 32437.30

4.22x speedup

flex-datatype.x 31570.70

```

#### European Processor Initiative

### 3.2 Getting Extrae traces in the FPGA nodes

- We recommend using Extrae to trace the binaries running in the FPGA, but there are other methods (like PAPI), described in this guide.

- Send an Extrae job to the FPGA using the trace\_extrae\_fpga script:

```

synth-hca$ sbatch fpga_job trace_extrae_fpga ./flex-datatype.x

```

When the job finishes, copy the traces back to your machine and open them in Paraver

```

your-machine$ rsync -a user@ssh.hca.bsc.es:~/SDV_Tutorial/extrae_prv_traces .

your-machine$ wxparaver ./extrae_prv_traces/fpga-flex-datatype.prv

```

#### European Processor Initiative

### 3.2 Getting Extrae traces in the FPGA nodes

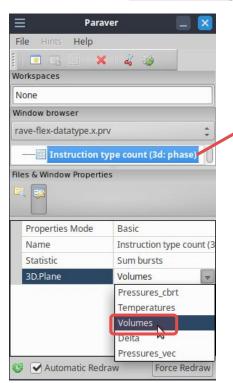

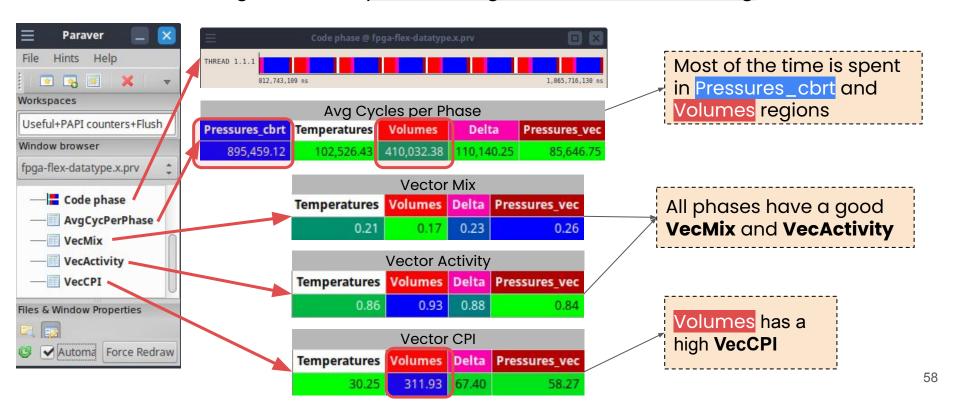

The configuration file paraver\_cfgs/extrae/PerfMetrics.cfg computes these vector metrics:

### 3.2 Getting Extrae traces in the FPGA nodes

Load the configuration file paraver\_cfgs/extrae/PerfMetrics.cfg

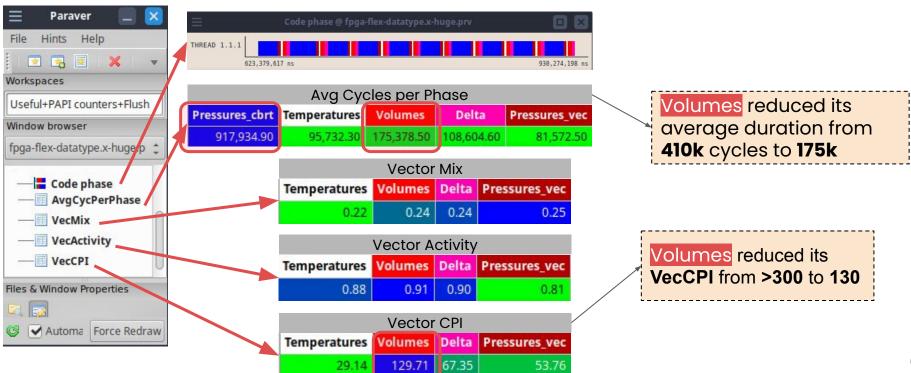

# 3.3 Using huge pages

- When a region with indexed/indirect access (like Volumes) has a large VecCPI it might be a TLB issue:

- The vector elements might be accessing more pages than there are entries in the TLB.

- The solution is to let the OS use huge pages (2MB) instead of 4KB pages.

- You can use the script in huge\_pages to execute your binary with huge pages.

- You can send an Extrae job using huge pages like this:

```

synth-hca$ sbatch fpga_job huge_pages run_extrae_fpga ./flex-datatype.x

```

When the job finishes, copy the traces back to your machine and open them

```

your-machine$ rsync -a user@ssh.hca.bsc.es:~/SDV_Tutorial/extrae_prv_traces .

your-machine$ wxparaver ./extrae_prv_traces/flex-datatype.x-huge.prv

```

# 3.3 Using huge pages

Load the configuration file paraver\_cfgs/extrae/PerfMetrics.cfg

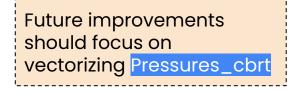

#### Conclusions

Improvement across versions:

- Using the SDV methodology we achieved a 5x speedup on the application

- Most of the time is spent on non-vectorized code

| %Time per Phase |              |         |        |               |

|-----------------|--------------|---------|--------|---------------|

| Pressures_cbrt  | Temperatures | Volumes | Delta  | Pressures_vec |

| 66.95 %         | 6.72 %       | 12.59 % | 7.78 % | 5.96 %        |

#### Acknowledgment

This research has received funding from the European High Performance Computing Joint Undertaking (JU) under Framework Partnership Agreement No 800928 (European Processor Initiative) and Specific Grant Agreement No 101036168 (EPI SGA2). The JU receives support from the European Union's Horizon 2020 research and innovation programme and from Croatia, France, Germany, Greece, Italy, Netherlands, Portugal, Spain, Sweden, and Switzerland. The EPI-SGA2 project, PCI2022-132935 is also co-funded by MCIN/AEI /10.13039/501100011033 and by the UE NextGenerationEU/PRTR.

Don't hesitate to contact me at pablo.vizcaino@bsc.es!